平成21年 秋期 基本情報技術者 午後 問01

問01 5問選択半加算器と全加算器に関する次の記述を読んで,設問1~3に答えよ。

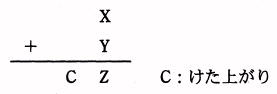

(1) 1ビット同士を加算する半加算器の真理値表を,表1に示す。

| Ⅹ | Y |  |

C | Z |

| 0 | 0 |  | 0 | 0 |

| 0 | 1 |  | 0 | 1 |

| 1 | 0 |  | 0 | 1 |

| 1 | 1 |  | 1 | 0 |

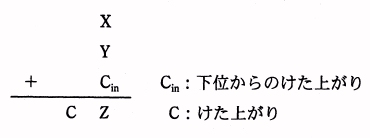

(2) 下位からのけた上がり Cin を考慮して1ビット同士を加算する全加算器の真理値表を,表2に示す。

| Cin | X | Y |  | C | Z |

| 0 | 0 | 0 |  | 0 | 0 |

| 0 | 0 | 1 |  | 0 | 1 |

| 0 | 1 | 0 |  | 0 | 1 |

| 0 | 1 | 1 |  | 1 | 0 |

| 1 | 0 | 0 |  | 0 | 1 |

| 1 | 0 | 1 |  | 1 | 0 |

| 1 | 1 | 0 |  | 1 | 0 |

| 1 | 1 | 1 |  | 1 | 1 |

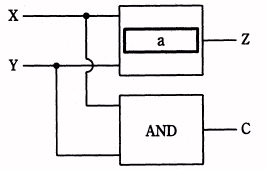

設問1 半加算器を実現する論理回路を,図1に示す。図1中の  に入れる正

しい答えを,解答群の中から選べ。ただし,AND は論理積,OR は論理和,XOR は排他的論理和,

NAND は否定論理積,NOR は否定論理和を表す。

に入れる正

しい答えを,解答群の中から選べ。ただし,AND は論理積,OR は論理和,XOR は排他的論理和,

NAND は否定論理積,NOR は否定論理和を表す。

図1 半加算器を実現する論理回路

解答群

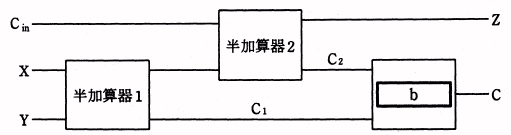

設問2 全加算器を実現する論理回路について, 次の記述中の

に入れる正しい答えを,解答群の中から選べ。

に入れる正しい答えを,解答群の中から選べ。

全加算器は,図2に示すように半加算器を2段に接続して実現する。半加算器1はXとYを加算し, 半加算器2は半加算器1の結果と Cin を加算する。このとき, 半加算器1のけた上がりを C1,半加算器2のけた上がりを C2 とする。 X,Y, Cin と, C1, C2 との関係は表3のとおりになる。

図2 全加算器を実現する論理回路

| Cin | X | Y |  | C1 | C2 |

| 0 | 0 | 0 |  | 0 | 0 |

| 0 | 0 | 1 |  | 0 | 0 |

| 0 | 1 | 0 |  | 0 | 0 |

| 0 | 1 | 1 |  | 1 | 0 |

| 1 | 0 | 0 |  | 0 | 0 |

| 1 | 0 | 1 |  | 0 | 1 |

| 1 | 1 | 0 |  | 0 | 1 |

| 1 | 1 | 1 |  |  | |

b に関する解答群

| C1 | C2 | |

| ア | 0 | 0 |

| イ | 0 | 1 |

| ウ | 1 | 0 |

| エ | 1 | 1 |

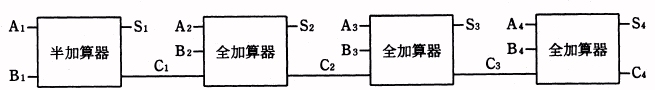

設問3 A,B 及び S を2の補数表現による4ビットの符号付2進整数とし,それぞれの ビット表現を A4A3A2A1, B4B3B2B1,及び S4S3S2S1で表す(符号ビットは A4,B4及び S4)。

図3は,A と B の加算を行い,結果を S に求める加算器であり,半加算器と全 加算器で実現されている。ここで,C1~C4 とは半加算器及び全加算器からのけた 上がりを表す。

この加算器に,A として-1 を,B として-2(いずれも 10 進表記)を与えたとき, 図3のC1~C4の値として正しい組合せを,解答群の中から選べ。

図3 A と B を加算して S を求める加算器

解答群

| C1 | C2 | C3 | C4 | |

| ア | 0 | 1 | 0 | 0 |

| イ | 0 | 1 | 0 | 1 |

| ウ | 0 | 1 | 1 | 0 |

| エ | 0 | 1 | 1 | 1 |

| オ | 1 | 0 | 0 | 0 |

| カ | 1 | 0 | 0 | 1 |

| キ | 1 | 0 | 1 | 0 |

| ク | 1 | 0 | 1 | 1 |

[←前の問題] [次の問題→] [問題一覧表] [分野別] [基本情報技術者試験TOP ]

©2004-2025 情報処理試験.jp

|

プライバシーポリシー・著作権・リンク

|

お問合わせ